# ISL91117II7-EVZ, ISL91117IIA-EVZ Evaluation Boards

### **Description**

The ISL91117 is a highly-integrated boost switching regulator for battery powered applications. The device provides a power supply solution for products using dual-cell or three-cell alkaline, NiCd or NiMH, or one-cell Li-ion or Li-polymer battery The ISL91117II7-EVZ and ISL91117IIA-EVZ platforms allow quick evaluation of the high performance features of the ISL91117 high current boost regulator series.

#### **Specifications**

The boards are designed to operate at the following operating conditions:

- · Input voltage rating from 1.8V to 4.8V

- Resistor programmable output voltage on the ISL91117IIA-EVZ

- Fixed 5V output voltage on the ISL91117II7-EVZ

- · True disconnect input to output when disabled

- Up to 1.5A output current (PVIN = 3.3V, V<sub>OUT</sub> = 5V)

- · 2.5MHz switching frequency

- Operating temperature range: -40°C to +85°C

#### **Key Board Features**

- · Small, compact design

- Jumper selectable EN (enabled/disabled)

- Jumper selectable MODE (auto-PFM/forced-PWM)

- · Connectors, test points, and jumpers for easy probing

#### References

ISL91117 Data Sheet.

#### **Ordering Information**

| PART NUMBER     | DESCRIPTION                       |  |

|-----------------|-----------------------------------|--|

| ISL91117II7-EVZ | Evaluation Board for ISL91117II7Z |  |

| ISL91117IIA-EVZ | Evaluation Board for ISL91117IIAZ |  |

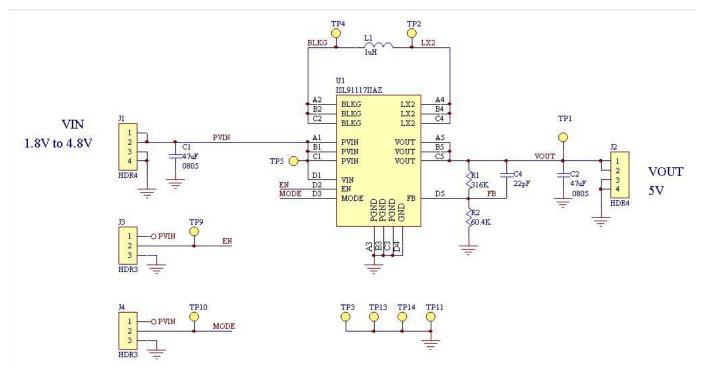

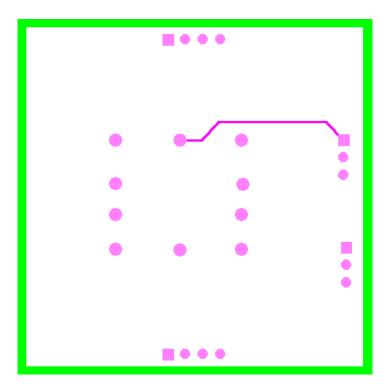

FIGURE 1. ISL91117IIA-EVZ BLOCK DIAGRAM

#### **Functional description**

The ISL91117II7-EVZ and ISL91117IIA-EVZ evaluation boards provide simple platforms to demonstrate the feature of the ISL91117 high current boost regulator. The ISL91117II7-EVZ is for the fixed 5V output IC ISL91117II7Z and the ISL91117IIA-EVZ is for the adjustable output IC ISL91117IIAZ. The evaluation boards have been functionally optimized for best performance of the ISL91117 IC series. The input power and load connections are provided through multi-pin connectors for high current operations.

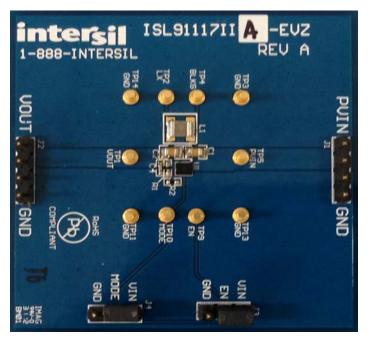

The ISL91117IIA-EVZ evaluation board is shown in Figures 4 and 5. The board's enable function is controlled by the on-board jumper header J3. Similarly the Mode function is controlled by the on-board jumper header J4.

The schematic of the ISL91117IIA-EVZ evaluation board is shown in Figure 6. The schematic for the ISL91117II7-EVZ is shown in Figure 7. The PCB layout images for all layers are shown in Figures 8 through 11. The bill of materials of the ISL91117IIA-EVZ is shown in Table 2. The bill of materials of the ISL91117II7-EVZ is shown in Table 3.

#### **Operating Range**

The V<sub>IN</sub> range of the boards is 1.8V to 4.8V. The V<sub>OUT</sub> range for the ISL91117IIA-EVZ is V<sub>IN</sub>+0.2V to 5V. The I<sub>OUT</sub> range of the boards is 0 to 1.5A. The operating ambient temperature range is -40 °C to +85 °C.

#### **Quick Start Guide**

For the ISL91117IIA-EVZ board, the default output voltage is set at 5V. Should other output voltages are desired, resistor R1 can be changed to set to a desired voltage as shown in Table 1 (use a resistor with 1% accuracy).

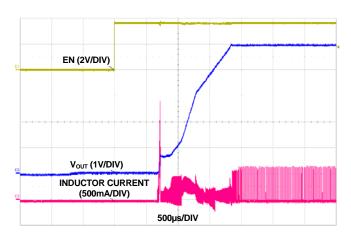

Refer to the following Quick Setup Guide to configure and power up the board for proper operation. During the power on process, the expected waveforms are shown in Figures 2 and 3.

#### **Quick Setup Guide**

- 1. Install jumper on J3, shorting EN to VIN.

- 2. Install jumper on J4, shorting MODE to VIN.

- Connect power supply to J1, with voltage setting between 1.8V and 4.8V.

- 4. Connect electronic load to J2.

- 5. Place scope probes on the  $V_{\mbox{\scriptsize OUT}}$  test point, and other test points of interest.

- 6. Turn on the power supply.

- 7. Monitor the output voltage start-up sequence on the scope. The waveforms will look similar to that shown in Figure 2.

- 8. Turn on the electronic load.

- Measure the output voltage with the voltmeter. The voltage should regulate within datasheet spec limits.

- 10. To determine efficiency, measure input and output voltages at the Kelvin sense test points (S+ and S-), which are part of J1 and J2 headers. The bench power supply can be connected to the PVIN and GND headers on J1. The electronic load can be connected to the VOUT and GND headers on J2. Measure

- the input and output currents. Calculate efficiency based on these measurements.

- 11. To test external sync, remove the jumper at J4, then apply an external clock between 2.75MHz and 3.25MHz on the MODE input (the center pin of header J4).

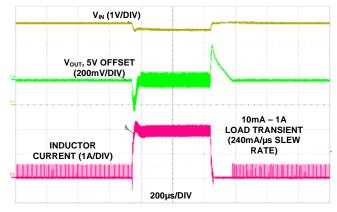

- 12. Set the electronic load to constant current dynamic mode with 10mA to 1A pulse,  $t_{\rm ON}$ = 500 $\mu$ s. Check the load transient response as shown in Figure 3.

TABLE 1. OUTPUT VOLTAGE PROGRAMMING For ISL91117IIA-EVZ

| DESIRED OUTPUT VOLTAGE (V) | R1 RESISTOR VALUES (kΩ) |

|----------------------------|-------------------------|

| 2.0                        | 90.9                    |

| 2.5                        | 127                     |

| 3.0                        | 165                     |

| 3.3                        | 187                     |

| 3.6                        | 210                     |

| 4.0                        | 243                     |

| 4.5                        | 280                     |

| 5.0                        | 316                     |

FIGURE 2. ISL91117 START-UP WITH  $V_{IN} = 3.6V$  and  $V_{OUT} = 5V$

FIGURE 3. ISL91117 LOAD TRANSIENT AT  $V_{IN}$  = 3V AND  $V_{OUT}$  = 5V

### **ISL91117IIA-EVZ Evaluation Board**

FIGURE 4. TOP VIEW

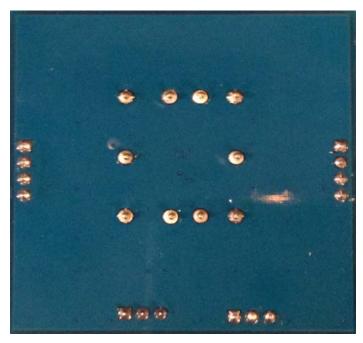

FIGURE 5. BOTTOM VIEW

## **ISL91117IIA-EVZ Evaluation Board Schematic**

FIGURE 6. ISL91117IIA-EVZ EVALUATION BOARD SCHEMATIC

#### TABLE 2. ISL91117IIA-EVZ EVALUATION BOARD BILL OF MATERIALS

| ITEM# | QTY | DESIGNATORS                                           | PART TYPE                  | FOOTPRINT      | DESCRIPTION                                                      | VENDORS       |

|-------|-----|-------------------------------------------------------|----------------------------|----------------|------------------------------------------------------------------|---------------|

| 1     | 1   | U1                                                    | ISL91117IIAZ               | W4x5.20; WLCSP | Intersil ISL91117 Boost Regulator with Adjustable Output Voltage | INTERSIL      |

| 2     | 1   | L1                                                    | <b>1</b> μΗ                | 3.2mmx2.5mm    | Power Inductor DFE322512C, 4.6A, 34mΩ                            | токо          |

| 3     | 2   | C1, C2                                                | 47μF/6.3V/<br>X5R          | 0805           | Capacitor, GRM21BR60J476ME15L                                    | MURATA        |

| 4     | 1   | C4                                                    | 22pF                       | 0402           | Capacitor, Generic                                               | ANY           |

| 5     | 1   | R1                                                    | <b>316k</b> Ω, <b>1</b> %  | 0402           | Resistor, Generic                                                | ANY           |

| 6     | 1   | R2                                                    | <b>60.4k</b> Ω, <b>1</b> % | 0402           | Resistor, Generic                                                | ANY           |

| 7     | 2   | J3, J4                                                | HDR-3                      | HDR-3          | Vert. Pin Header, 3-Pin, 0.1" Spacing, Generic                   | ANY           |

| 11    | 2   | J1, J2                                                | HDR-4                      | HDR-4          | Vert. Pin Header, 4-Pin, 0.1" Spacing, Generic                   | ANY           |

| 12    | 9   | TP1, TP2, TP4, TP5,<br>TP9, TP10, TP11,<br>TP13, TP14 | TEST POINT                 | TEST POINT     | Test Point, Thru-Hole, 3156-1-00-15-00-00-08-0                   | MILL-MAX PINS |

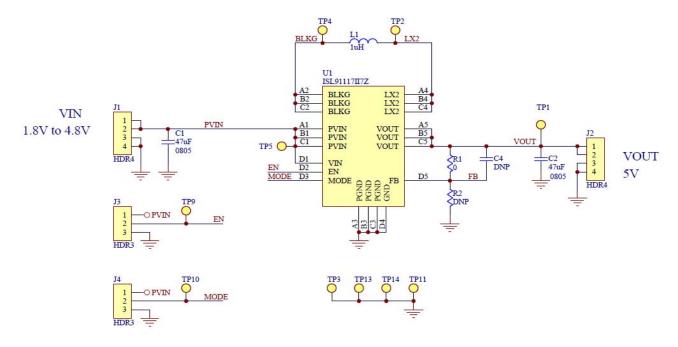

## **ISL91117II7-EVZ Evaluation Board Schematic**

FIGURE 7. ISL91117II7-EVZ EVALUATION BOARD SCHEMATIC

TABLE 3. ISL91117II7-EVZ EVALUATION BOARD BILL OF MATERIALS

| ITEM# | QTY | DESIGNATORS                                           | PART TYPE     | FOOTPRINT        | DESCRIPTION                                               | VENDORS       |

|-------|-----|-------------------------------------------------------|---------------|------------------|-----------------------------------------------------------|---------------|

| 1     | 1   | U1                                                    | ISL91117II7Z  | W4x5.20<br>WLCSP | Intersil ISL91117 Boost Regulator with Fixed 5V<br>Output | INTERSIL      |

| 2     | 1   | L1                                                    | 1μΗ           | 3.2mmx2.5mm      | Power Inductor DFE322512C, 4.6A, 34mΩ                     | токо          |

| 3     | 2   | C1, C2                                                | 47μF/6.3V/X5R | 0805             | Capacitor, GRM21BR60J476ME15L                             | MURATA        |

| 4     | 1   | C4                                                    | OPEN          | 0402             | Not installed                                             | ANY           |

| 5     | 1   | R1                                                    | Ω0            | 0402             | Resistor, Generic                                         | ANY           |

| 6     | 1   | R2                                                    | OPEN          | 0402             | Not installed                                             | ANY           |

| 7     | 2   | J3, J4                                                | HDR-3         | HDR-3            | Vert. Pin Header, 3-Pin, 0.1" Spacing, Generic            | ANY           |

| 11    | 2   | J1, J2                                                | HDR-4         | HDR-4            | Vert. Pin Header, 4-Pin, 0.1" Spacing, Generic            | ANY           |

| 12    | 9   | TP1, TP2, TP4, TP5,<br>TP9, TP10, TP11,<br>TP13, TP14 | TEST POINT    | TEST POINT       | Test Point, Thru-Hole, 3156-1-00-15-00-00-08-0            | MILL-MAX PINS |

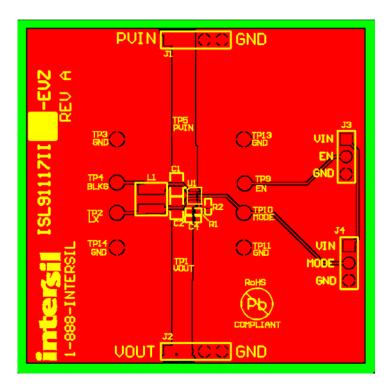

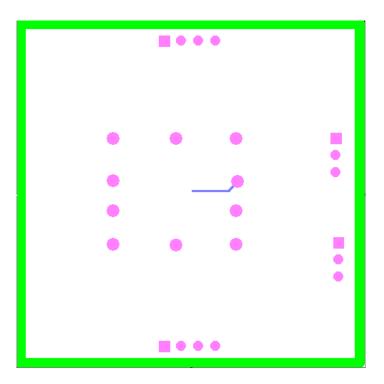

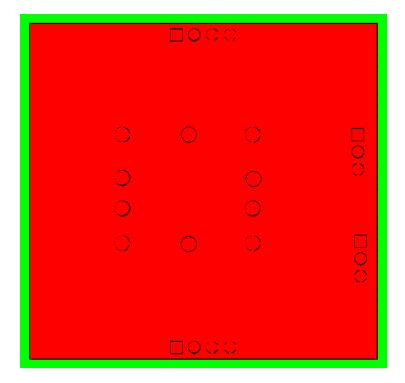

# **PCB Layout**

FIGURE 8. TOP LAYER

FIGURE 9. INNER LAYER 1

# PCB Layout (Continued)

FIGURE 10. INNER LAYER 2

FIGURE 11. BOTTOM LAYER

Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that the Application Note or Technical Brief is current before proceeding.

For information regarding Intersil Corporation and its products, see www.intersil.com  $\,$